# LECTURE NOTES Field Effect Transistor

**Branch: Electronics**

Semester: Second

Subject Teacher:

VISHWAJEET, Lecturer Electronics,

Mahamaya Polytechnic of Information Technology,

Salempur, Hathras

#### **Field Effect Transistor**

Field effect Transistor is a semiconductor device which depends for its operation on the control of current by an electric Field

#### **Field Effect Transistor**

FET has several advantages over BJT

- 1. Current flow is due to majority carriers only

- 2. Immune to radiation

- 3. High input resistance

- 4. Less noisy than BJT

- 5. No offset voltages at zero drain current

- 6. High thermal stability

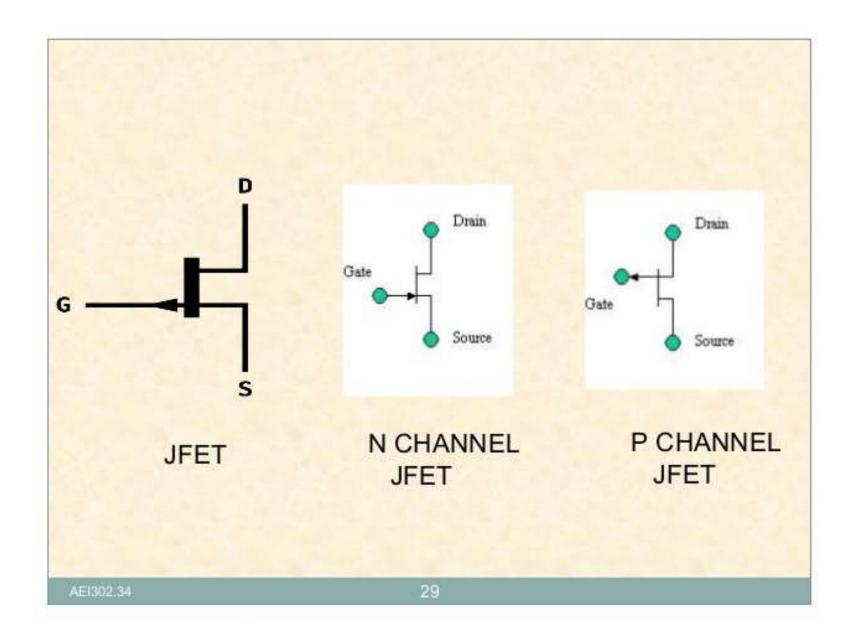

# JFET Symbol

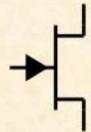

N Channel FET

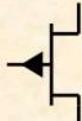

P Channel FET

Fig 4 . JFET symbols

AEI302.31 TO 33

Ø

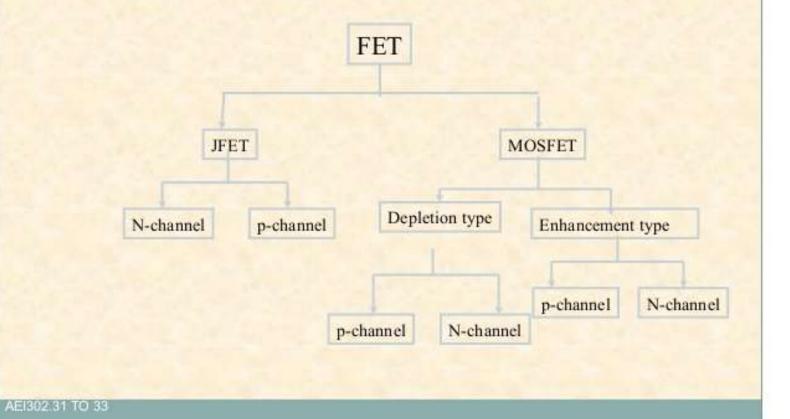

## **JFET**

Based on the construction JFETS are of Two types

1.N Channel FET

2.P Channel FET

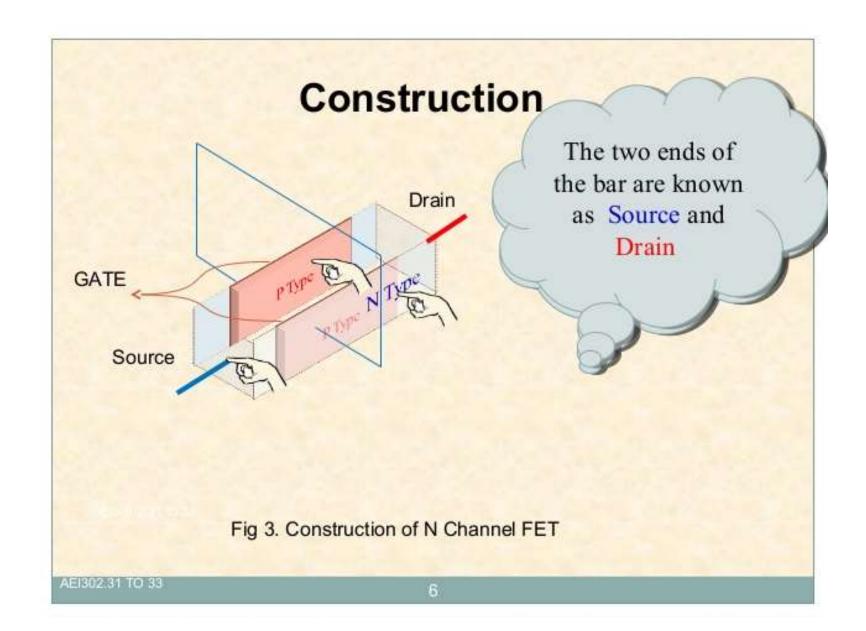

#### Construction of FET

Source: The source is the terminal through which majority carriers enter the Silicon Bar

Drain: Terminal through which Majoroty carriers leave the bar

Gate: controls Drain current and is always reverse biased

#### Construction of FET

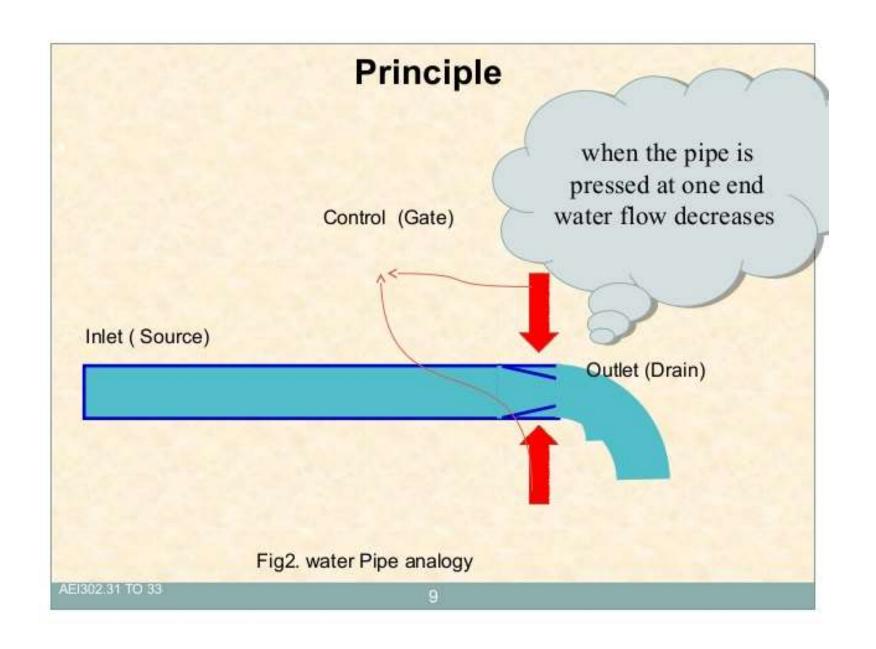

## Analogy:

- The operation of FET can be compared to the water flow through a flexible pipe

- ➤ When One end is pressed the cross sectional area decreases hence water flow decreases

- In a FET drain is similar to outlet

- Gate is similar to control in the figure 2

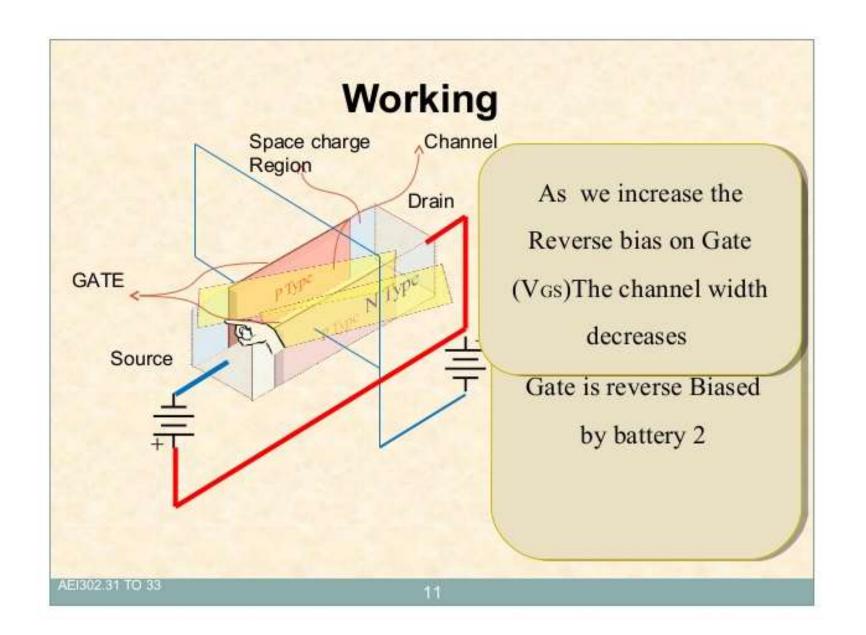

## Operation

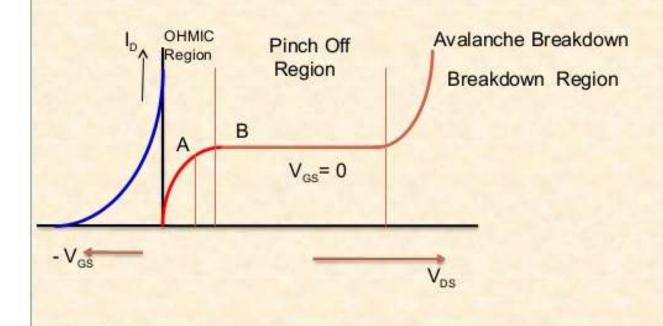

Principle: To control the drain current FET makes use of channel formed in by Space charge region between Gate and the bar

By increasing the reverse bias the width of space charge region decreases

As a result the channel Resistance increases

The Drain current decreases

The Bias voltage at which

Drain current becomes

Zero is Known as pinch

off voltage

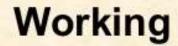

# Working

N Channel FET

Source connected to -VE

Drain Connected to +ve

Gate connected to -ve (Reverse Biased)

P Channel FET

Source connected to +VE

Drain Connected to -ve

Gate connected to +ve (Reverse Biased)

## Working

- when Voltage is applied between source and Drain majority carriers move through the channel between depletion region

- The value of Drain current is maximum when no external voltage is applied between gate and source

- When gate to source reverse bias increases the depletion region widens and channel width decreases hence Drain current decreases

## Working

- 1. Hence Drain current decreases

- When gate to source voltage is increased further The channel completely closes

- 3. This is called pinch off region

- 4. This reduces Drain current to Zero

- The Gate to source voltage at which the Drain current is zero is called "Pinch off Voltage"

# P Type and N type FETs

#### N Channel FET

- Current carriers are Electrons

- 2. Mobility of electrons is almost twice that of Holes in P channel FET

- 3. Low input Noise

- 4. Large Transconductance

#### P Channel FET

- 1. Current carriers are holes

- 2. Mobility of holes is poor

- 3.More noise

- 4.Low Transconductance

Electrical behavior is described in terms of the parameters of the Device. They are obtained from the characteristics. Important Parameters for FET are

- 1.DC Drain resistance

- 2.AC drain Resistance

- 3. Transconductance

- DC Drain resistance: Defined as Ratio of Drain to source Voltage V<sub>DS</sub> to Drain current I<sub>D</sub>. Also called static or Ohmic Resistance

- 2. Mathematically

$$R_{DS} = V_{DS}/I_{D}$$

- AC Drain resistance: Defined as the resistance between Drain to source when JFET is operating in Pinch off Region or saturation Region

- 2. Mathematically

$$r_D = \frac{\Delta V_{DS}}{\Delta I_D}$$

When  $V_{\rm gs}$  is constant

Transconductance (g<sub>m</sub>): It is given by the ratio

of small change in drain current to the

corresponding change in the Gate to source

Voltage VGS. Also known as Forward

Transmittance

2. Mathematically

$$g_m = \frac{\Delta I_D}{\Delta V_{DS}}$$

#### **FET and BJT**

#### FET

- 1. Uni polar device

- 2. Voltage controlled Device

- High input impedance (in Mega ohms)

- 4. Better thermal stability

- 5. High switching speeds

- 6. Less Noisy

- 7. Easy to fabricate

#### BJT

- Bipolar device

- 2. Current controlled device

- 3.Low input impedance

- 4.Low thermal stabilty

- 5.Lower switching speeds

- 6. More noisy

- 7. Diffuicult to fabricate on IC

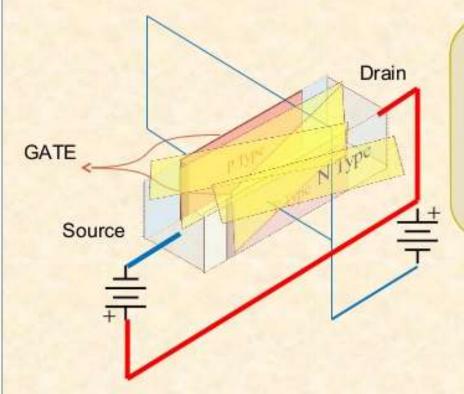

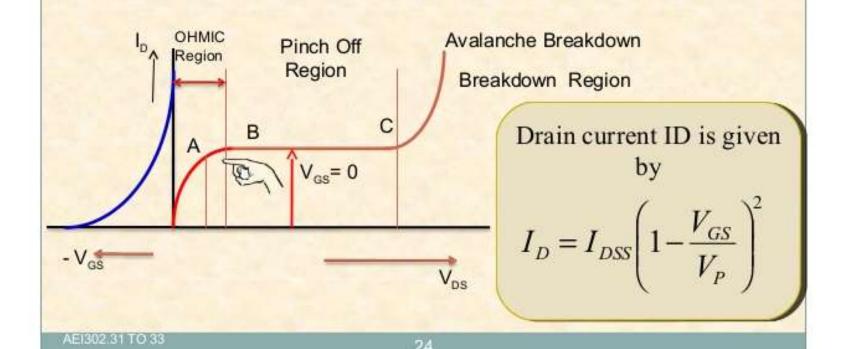

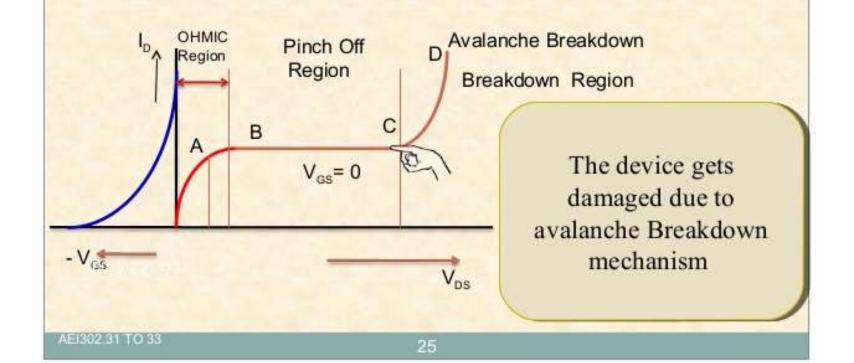

Drain characteristics show the relation between the drain to source voltage and VDS and drain current ID

22

Drain characteristics show the relation between the drain to source voltage and VDS and drain current ID

Drain characteristics show the relation between the drain to source voltage and VDS and drain current ID

Drain characteristics show the relation between the drain to source voltage and VDS and drain current ID

#### DISADVANTAGES OF FET OVER BJT

FETs have a drawback of smaller gain bandwidth product compared to BJT.

#### **Features**

• The high input impedance, low output impedance and low noise level make FET for superior of the bipolar transistor.

## Applications

As a buffer amplifier which isolates the preceding stage from the following stage.

#### **FET APPLICATIONS**

Phase shift oscillators: The high input impedance of FET is especially valuable in phase shift oscillator to minimize the loading effect.

In voltmeters: The high input impedance of FET is useful in voltmeters to act as an input stage.